verilog编程问题,找出一个数据中的第一个'1'

发布时间:2025-05-24 23:43:26 发布人:远客网络

一、verilog编程问题,找出一个数据中的第一个'1'

1、功能实现出来是个具有优先级的选择器

2、否则如果data[1]=1则data_out=1<<1;

3、否则如果data[i]=1则data_out=1<<i

4、如果使用支持verilog的for循环语句的综合器可以写成

5、if(data[i]) data_out= 1<<i;

6、功能看起来很简单但是延迟不小资源也不少

7、如果对延迟有要求可以考虑用查找表就是把对应的data的镜像(data[0:31])当作索引选择出相应的结果

8、32'hFFFF_FFFF,..., 32'h8000_0000: data_out= 32'h8000_0000;

9、遗憾的是 verilog不支持case项的范围可以考虑用systemverilog语法中的inside语句(现在多数综合器都支持)或者vhdl语法(所有综合器都支持但是vhdl日渐势微)

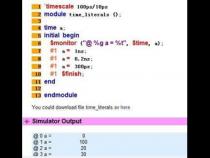

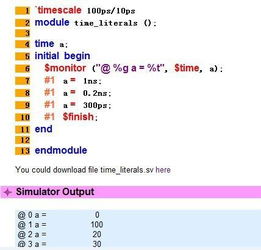

二、verilog问题,能解释下为什么是这个答案吗

1、在casez语句中,如果分支表达式某些位的值为高阻z,那么对这些位的比较就会忽略,不予考虑,而只关注其他位的比较结果。

2、在casex语句中,则把这种处理方式进一步扩展到对x的处理,即如果比较双方有一方的某些位的值是z或x,那么这些位的比较就不予考虑。

3、题中5‘b0X000的X不考虑,所以与之匹配的是5’b00???。A的值为1,B的值不变

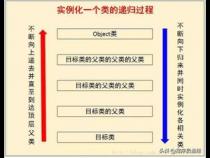

三、verilog编程的问题

1、你说的两个模块之间的实例化吧,在图形上就是用线连起来,我教你。

2、比如有两个模块定义为:moudle A和moudle B

3、其中A模块有一个输出信号设为:output a1,a2;

4、 B模块有一个输入信号设为:input b1,b2;

5、那么当我们需要将a1,a2连到b1,b2(用debussy看的话也就是一条连线),这个就要实例化A和B这两个模块,具体是这么写的:

6、这段代码放到A模块的最后,endmoudle之前就行。

7、其中B_LianJie是我们自己随便起的实例化的名字,B指的是调用B这个模块进行实例化。

8、如要将这段代码放到B模块里,那么就得调用A模块来实例化:

9、这样就把我们需要连接的两个模块连到一起了,信号多了也是一样的,继续把信号对应填到括号里就行了。

10、如果还有不明白的,可以继续问我。verilog设计我做了2年了,呵呵。